時(shí)間:

瀏覽次數(shù):

在DesignCon 2020大會(huì)上,ANSYS舉辦了一系列贊助演講。我參加了其中的幾場(chǎng)。這些活動(dòng)都是由才華橫溢、精力充沛的演講者用他們的材料進(jìn)行精彩的展示。DesignCon技術(shù)方案具有超前的緯度。其中一個(gè)是由喬治亞理工學(xué)院電子與計(jì)算機(jī)工程學(xué)院的Sung-Kyu Lim教授提出的——這個(gè)演示涉及到3D集成電路。

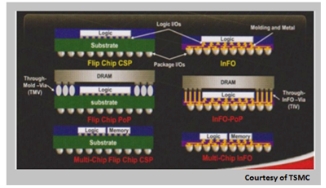

Lim教授的研究由DARPA、Arm和ANSYS資助。該討論集中在用Arm A7和A53處理器構(gòu)建的3D集成電路的熱分析、IR-drop和PPA分析上。因?yàn)?D IC可以代表很多東西,所以Lim教授的重點(diǎn)是光模堆積。他用這些技術(shù)審查了來自GLOBALFOUNDRIES、英特爾(Intel)和臺(tái)積電(TSMC)等公司的幾項(xiàng)設(shè)計(jì)。

首先,簡單介紹一下用于這些測(cè)試用例的設(shè)計(jì)流程。Lim教授在這里采取了一種實(shí)用的方法,將商業(yè)上可用的2D IC設(shè)計(jì)工具應(yīng)用于3D設(shè)計(jì)問題上。邏輯/內(nèi)存設(shè)計(jì)被分解成兩層,一層用于邏輯,另一層用于內(nèi)存。首先,內(nèi)存層被設(shè)計(jì)一個(gè)引腳分配層。然后創(chuàng)建了一個(gè)雙金屬堆棧。這允許內(nèi)存層和邏輯層通過使用硅穿孔TSV、面對(duì)面焊盤或單片層間通孔(MIV)通過密集連接進(jìn)行通信。接下來,邏輯層與來自內(nèi)存層的連接一起被放置和路由,這些連接也表示在邏輯層中。

該方法的結(jié)果討論了一個(gè)Arm Cortex A7設(shè)計(jì),包含L1, L2高速緩存和邏輯層。所有的L2和部分L1緩存被放置在內(nèi)存層,其余的設(shè)計(jì)在邏輯層實(shí)現(xiàn)。因此,緩存和邏輯之間的互連縮短了很多。類似的過程也應(yīng)用于Cortex A53的設(shè)計(jì)上。

由于采用了兩層方法,這些實(shí)驗(yàn)的結(jié)果占用的空間更小,而且由于路線更短,性能得到了改善。但反過來,由于更快的運(yùn)行速度導(dǎo)致了更大的功率,更高的紅外下降和增加的溫度,

此外,他們還進(jìn)行了節(jié)能實(shí)驗(yàn)。本例采用LDPC糾錯(cuò)電路。由于更短的電線長度和更小的電容器,這節(jié)省了39%的電能,這說明了3D設(shè)計(jì)的另一個(gè)優(yōu)點(diǎn)。

回到Arm的設(shè)計(jì),下面是2D和3D之間各種實(shí)驗(yàn)的熱圖,進(jìn)行熱比較。

然后,Lim教授討論了用于這些分析的工具流。其中說到被廣泛用于執(zhí)行許多任務(wù)的ANSYS RedHawk,包括功率,熱和紅外落差分析。所有這些工作都是基于對(duì)跨多個(gè)溫度配置文件的每個(gè)路由段和設(shè)備的細(xì)粒度分析。下圖是流程的概述。

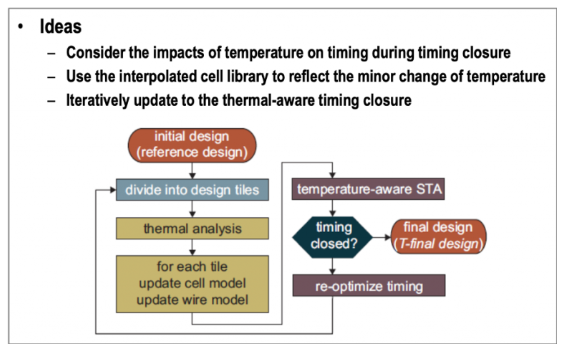

在演講的最后,Lim教授還討論了熱感知對(duì)集成電路設(shè)計(jì)的影響。他提出了一種溫度感知的定時(shí)閉合流,可以根據(jù)實(shí)際的溫度梯度來更新電路性能。這種方法可以產(chǎn)生在真實(shí)環(huán)境中更加有利的設(shè)計(jì)。

延伸閱讀——Ansys RedHawk

芯片封裝協(xié)同分析

在針對(duì)移動(dòng)手機(jī)或服務(wù)器的電子系統(tǒng)中,處理器和存儲(chǔ)器等 IC 負(fù)責(zé)執(zhí)行應(yīng)用程序和數(shù)據(jù)處理功能,消耗的功率最多。這些 IC 與它們的 I/O 電路之間輸入/輸出的數(shù)據(jù)量最大,并且產(chǎn)生的有害功率、熱量以及 EMI 信號(hào)也最大。

IC 消耗的功率與其電源電壓直接相關(guān)。由于閾值電壓不會(huì)一同縮放,電源和閾值電壓之間的差距縮小,從而降低了噪音容限。

隨著技術(shù)的發(fā)展,由于封裝阻抗日益增加,對(duì)降低成本和能耗的需求使芯片和封裝級(jí)別的供電網(wǎng)絡(luò) (PDN) 設(shè)計(jì)變得復(fù)雜。這減少了電壓,對(duì)芯片而言成為有害級(jí)別。

RedHawk-CPA 支持您無縫導(dǎo)入封裝布局,以及針對(duì)封裝感知和精確的片上靜態(tài) IR 以及交流熱點(diǎn)分析考慮去耦電容和電感。

熱感知 EM

ESD 及電源/接地和信號(hào) EM 是亞 16nm 級(jí)別最迫切需要解決的兩個(gè)可靠性問題。EM 和 ESD 分析的精確度以及覆蓋率極為重要。隨著導(dǎo)線中的電流增加,工作電壓會(huì)降低,EM 范圍會(huì)縮小。由于 FinFET 的使用,自熱被添加到熱問題中。在汽車等眾多應(yīng)用領(lǐng)域,了解、分析并優(yōu)化每個(gè) IC 設(shè)計(jì)以便實(shí)現(xiàn)正確熱行為至關(guān)重要。

RedHawk 為熱感知電源/接地和信號(hào)線 EM 驗(yàn)證提供全面支持,在盡量減少誤報(bào)的同時(shí)準(zhǔn)確分析 EM 沖突,即使是基于 FinFET 的先進(jìn)設(shè)計(jì)亦可從中受益。在與 Ansys PathFinder 結(jié)合使用時(shí),RedHawk 可以執(zhí)行 SoC 級(jí)別 ESD 完整性分析,從 ESD 事件(HBM、CDM)為所有電流通路(導(dǎo)線和過孔)提供連接性和互連故障檢查。RedHawk 在電源 EM、信號(hào) EM 和 SoC ESD 簽核方面獲得芯片代工廠認(rèn)證。

功能和容量

目前的片上系統(tǒng) (SoC) 擁有更大規(guī)模的整合內(nèi)容,并且采用先進(jìn)的工藝技術(shù)。因此,必須考慮的設(shè)計(jì)參數(shù)的數(shù)量正在迅速增加。這為執(zhí)行分析帶來了性能瓶頸:最好的情況是要運(yùn)行數(shù)天,最壞的情況是根本無法運(yùn)行。

RedHawk 采用先進(jìn)的分布式機(jī)器處理 (DMP) 技術(shù),可為您提供模擬包含超10 億個(gè)實(shí)例的設(shè)計(jì)所需的大容量和高性能。DMP 擁有的簽核精確度僅可通過扁平仿真獲得。

DMP 還利用私有機(jī)器群集不斷增強(qiáng)的處理能力和可用存儲(chǔ)容量,對(duì)整個(gè)芯片的 RLC 網(wǎng)絡(luò)矩陣進(jìn)行仿真,并使用完全分布式和交叉耦合的封裝模型。通過執(zhí)行全芯片扁平分析,RedHawk 能夠保持動(dòng)態(tài)降壓、EM 和 ESD 的簽核精確度。

經(jīng)過硅驗(yàn)證的簽核精確度

在芯片級(jí)別,對(duì)最新工藝技術(shù)的使用往往受到以下一個(gè)或多個(gè)因素的驅(qū)動(dòng):更快的性能、更大的帶寬、更高的性能功率比和更小的晶片尺寸。工藝技術(shù)越新,失敗的幾率越大,設(shè)計(jì)錯(cuò)誤造成的代價(jià)也就越高。這便是簽核認(rèn)證如此重要的原因。

自 2006 年以來,Ansys 工程師便在每個(gè)工藝技術(shù)方面與領(lǐng)先的晶圓代工廠展開緊密合作,確保 Ansys 解決方案考慮到工藝的所有新規(guī)則、參數(shù)和要求,并確保其結(jié)果與測(cè)試芯片的參考結(jié)果保持一致。

Ansys 多物理場(chǎng)解決方案經(jīng)過所有主要晶圓代工廠的所有進(jìn)階 FinFET 流程節(jié)點(diǎn)的驗(yàn)證,包括 TSMC 最近的 5nm 流程技術(shù)。晶圓代工廠認(rèn)證包括針對(duì)自發(fā)熱、熱感應(yīng) EM 的提取、電源完整性和可靠性、信號(hào)電遷移 (信號(hào) EM) 和熱可靠性分析以及統(tǒng)計(jì) EM 預(yù)算 (SEB) 分析。這些嚴(yán)格的認(rèn)證對(duì)于保證一次通過的硅晶至關(guān)重要。

電源噪音對(duì)時(shí)序的影響

設(shè)計(jì)中的動(dòng)態(tài)壓降可能對(duì)時(shí)鐘抖動(dòng)、關(guān)鍵路徑和時(shí)序產(chǎn)生影響。如今的設(shè)計(jì)擁有多個(gè)時(shí)鐘和電源域,在簽核前對(duì)時(shí)鐘樹的性能進(jìn)行評(píng)估,識(shí)別并分析抖動(dòng)、信號(hào)串?dāng)_和時(shí)序問題便非常重要。

RedHawk 的快速全芯片級(jí)時(shí)序影響分析可幫助您評(píng)估時(shí)鐘樹性能。此外,它還支持您對(duì)可能受抖動(dòng)、信號(hào)串?dāng)_和時(shí)序問題影響的電路零部件進(jìn)行識(shí)別。RedHawk 的 SPICE 精確簽核仿真可幫助您識(shí)別時(shí)鐘樹、受影響的關(guān)鍵路徑和電路時(shí)序的問題,并采取措施消除這些問題。

高級(jí) IC 封裝的完整性與可靠性

對(duì)包括片上系統(tǒng) (SoC) 在內(nèi)的集成電路 (IC) 設(shè)計(jì)師而言,有一個(gè)持續(xù)的策略,就是通過集成化和小型化,在增加性能和帶寬的同時(shí)降低能耗和占用面積。

對(duì)于任何封裝技術(shù),完整性、可靠性和成本都是需要優(yōu)化的三大主要因素。完整性因素涉及電源和信號(hào)噪音。可靠性涉及熱、電遷移 (EM)、靜電釋放 (ESD)、電磁干擾 (EMI) 和熱致結(jié)構(gòu)應(yīng)力問題。成本則涉及幾乎所有應(yīng)用,尤其是消費(fèi)品和物聯(lián)網(wǎng) (IoT) 設(shè)備。在每種芯片的封裝、電路板和系統(tǒng)的背景下優(yōu)化和確保芯片(晶片級(jí)別)的完整性和可靠性,這非常復(fù)雜,并且涉及多個(gè)晶片時(shí)成本只會(huì)增加。

Ansys 解決方案使您能夠確保您先進(jìn)的 2.5D 或 3D-IC 封裝設(shè)計(jì)可滿足芯片、封裝和系統(tǒng)級(jí)別的完整性和可靠性要求。Ansys 解決方案符合所有先進(jìn)的 3D-IC 封裝技術(shù),包括 TSMC 最新的 CoWoS、InFO_MS 以及 SoIC 封裝技術(shù)。Ansys 針對(duì)先進(jìn)封裝技術(shù)的多物理場(chǎng)解決方案能夠進(jìn)行多模具聯(lián)合模擬和聯(lián)合分析,實(shí)現(xiàn)提取、電源和信號(hào)集成分析、電源和信號(hào)電遷移分析、熱量和熱導(dǎo)壓力分析。

什么是TSV封裝?

3D IC技術(shù)蓬勃發(fā)展的背后推動(dòng)力來自消費(fèi)市場(chǎng)采用越來越復(fù)雜的互連技術(shù)連接硅片和晶圓。這些晶圓包含線寬越來越窄的芯片。

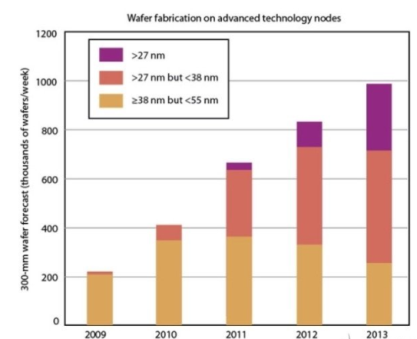

為了按比例縮小半導(dǎo)體IC,需要在300mm的晶圓上生成更精細(xì)的線條。據(jù)市場(chǎng)研究機(jī)構(gòu)VLSI Research預(yù)測(cè),雖然目前大多數(shù)量產(chǎn)的IC是基于55nm或55nm以下的設(shè)計(jì)節(jié)點(diǎn),但這些設(shè)計(jì)規(guī)則將縮小至38nm或更小,到2013年甚至?xí)s小到27nm。

硅通孔技術(shù)(Through Silicon Via, TSV)技術(shù)是一項(xiàng)高密度封裝技術(shù),正在逐漸取代目前工藝比較成熟的引線鍵合技術(shù),被認(rèn)為是第四代封裝技術(shù)。TSV技術(shù)通過銅、鎢、多晶硅等導(dǎo)電物質(zhì)的填充,實(shí)現(xiàn)硅通孔的垂直電氣互連。硅通孔技術(shù)可以通過垂直互連減小互聯(lián)長度,減小信號(hào)延遲,降低電容/電感,實(shí)現(xiàn)芯片間的低功耗,高速通訊,增加寬帶和實(shí)現(xiàn)器件集成的小型化。基于TSV技術(shù)的3D封裝主要有以下幾個(gè)方面優(yōu)勢(shì):

1)更好的電氣互連性能,

2)更寬的帶寬,

3)更高的互連密度,

4)更低的功耗,

5)更小的尺寸,

6)更輕的質(zhì)量。

TSV工藝主要包括深硅刻蝕形成微孔,絕緣層/阻擋層/種子層的沉積,深孔填充,化學(xué)機(jī)械拋光,減薄、pad的制備及再分布線制備等工藝技術(shù)。主要工藝包括幾個(gè)部分:

(1)通孔的形成;

(2)絕緣層、阻擋層和種子層的淀積;

(3)銅的填充(電鍍)、去除和再分布引線(RDL)電鍍;

(4)晶圓減薄;

(5)晶圓/芯片對(duì)準(zhǔn)、鍵合與切片。

TSV深孔填充技術(shù)是3D集成的關(guān)鍵技術(shù),也是難度較大的一個(gè)環(huán)節(jié),TSV填充效果直接關(guān)系到集成技術(shù)的可靠性和良率等問題,而高的可靠性和良率對(duì)于3D TSV 堆疊集成實(shí)用化是至關(guān)重要的。另外一個(gè)方面為在基片減薄過程中保持良好的完整性,避免裂紋擴(kuò)展是TSV工藝過程中的另一個(gè)難點(diǎn)。

TSV技術(shù)本質(zhì)上并不是一種封裝技術(shù)方案,而只是一種重要的工具,它允許半導(dǎo)體裸片和晶圓以較高的密度互連在一起。基于這個(gè)原因,TSV在大型IC封裝領(lǐng)域中是一個(gè)重要的步驟。但TSV不是推動(dòng)3D封裝技術(shù)進(jìn)步的唯一方法。它們僅代表眾多材料、工藝和封裝開發(fā)的一個(gè)部分。

未來的3D堆棧可能包含處理器、存儲(chǔ)器、邏輯和模擬及RF電路,所有這些都通過TVS互連。流體通過MEMS微通道實(shí)現(xiàn)冷卻。

相關(guān)推薦